Neuentwicklungen in der Elektronik werden heutzutage immer mehr von den EMV-Anforderungen dominiert. Erhebliche Folgekosten für die Produktentwicklung entstehen, weil Baugruppen die EMV-Tests nicht bestehen. Für die EMV der gesamten Elektronik sind die verwendeten ICs bestimmend. Diese sind als Ursache von Störaussendung oder als Schwachstellen der Störfestigkeit schwer in den Griff zu bekommen.

Die Strukturen von ICs sind im Laufe der Zeit immer kleiner geworden. Dadurch steigen ihre Schaltgeschwindigkeiten und die Versorgungsspannung musste verringert werden. Durch diese beiden Faktoren steigt ihre Empfindlichkeit gegenüber ESD.

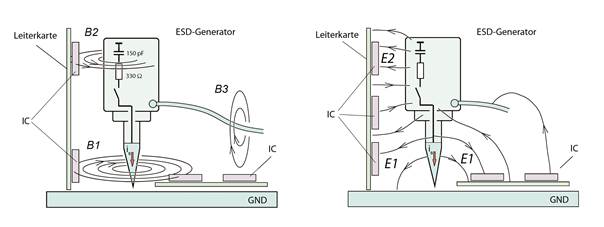

Bei EMV-Prüfungen nach Norm IEC 64000-4-2 werden elektronische Geräte mit einem ESD-Generator (ESD-Pistole) getestet. Der ESD-Generator erzeug nach Norm einen Stromimpuls, der in den Prüfling eingeleitet wird (Bild 1). Der ESD-Störpuls wird auf metallische Teile des elektronischen Gerätes eingekoppelt. Von dort gelangt er feld- und leitungsgebunden zum IC. Dabei wird der zum IC gelangende Störimpuls in seiner Amplitude und Zeitverlauf gewandelt. Ziel des Beitrages ist es, die Koppelwege zum IC aufzuklären. Für die einzelnen Koppelwege werden die am IC wirkenden Störimpulse in ihrer Amplitude und ihrem Verlauf gemessen. Es wird ermittelt, welche Kopplung relevant ist und welche Parameter (Steilheit, Spannungshöhe, Kurvenform, Amplitude, Strom, Spannung elektrisches oder magnetisches Feld) den Koppelvorgang beeinflussen. Mit diesen Erkenntnissen lassen sich gezielt EMV-Gegenmaßnahmen zum Schutz des ICs entwickeln.

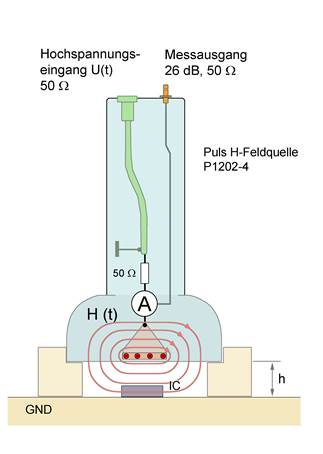

Zusätzlich zum Stromimpuls nach Norm, erzeugt der ESD-Generator ein magnetisches und elektrisches Feld (Bild 1). An der Spitze des ESD-Generators entsteht durch den Entladestrom ein magnetisches Wirbelfeld B1, das den IC und die Leitungsnetze der Baugruppe durchwirbelt. In Leitungsschleifen, die vom Feld durchsetzt werden, wird Störspannung induziert. Diese Spannung überlagert sich den elektrischen Signalen der Elektronik und stört die Funktion des elektronischen Gerätes.

Die Spitze des ESD-Generators besitzt eine Induktivität. Der Entladestrom der ESD-Pistole erzeugt an dieser Induktivität einen Spannungsabfall. Dieser Spannungsabfall erzeugt ein elektrisches Feld E1. Es geht von der Spitze aus und endet im Prüfling auf den Leitungen und ICs (Bild 1). In die Leitungen und ICs wird damit ein Störstromimpuls übertragen und stört die Funktion des elektronischen Gerätes.

Zusätzlich zu dem nach Norm beschriebenen Störstromvorgang über die Spitze, treten aus dem Körper des ESD-Generators elektrische und magnetische Felder aus (Bild 1). Der zeitliche Verlauf dieser Felder kann vollkommen anders sein als der Verlauf des Vorgangs nach Norm. Diese Felder erzeugen einen zusätzlichen Störeinfluss auf das elektronische Gerät, die die Wirkung der gewollten Prüfstörgröße an der Spitze übersteigen können. Die Stärke der Wirkung dieser Felder hängt von der Positionierung des ESD-Generators zu den Baugruppen des Gerätes ab. Durch Drehen und Schwenken des ESD-Generators können zufällig Schwachstellen im Gerät beeinflusst werden. Die Funktionsfehler des Gerätes treten scheinbar chaotisch auf. Der Wirkzusammenhang ist für den Entwickler nicht mehr nachvollziehbar und analysierbar.

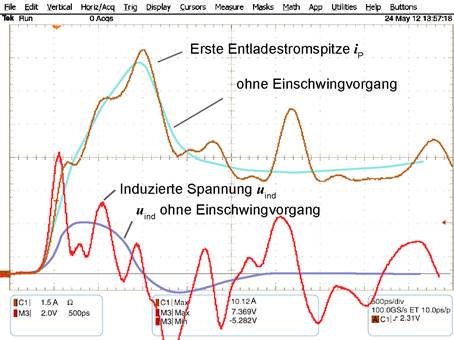

Im Bild 2 ist die erste Entladestromspitze des ESD-Generators vergrößert dargestellt. Man erkennt, dass auf der Vorderflanke mehrere Einschwingvorgänge liegen. Im Weiteren wird dieser Vorgang als ESD Einschwingvorgang bezeichnet. Die Entladestromspitze und der ESD Einschwingvorgang erzeugen einen magnetischen Fluss B1 (Bild 1) mit gleichem Zeitverlauf. Der magnetische Fluss B1 induziert in einer Leiterschleife der Elektronikbaugruppe eine Störspannung uind (Bild 2). Die Leiterschleife hat eine Größe von 8 mm2. Die eingestellte Spannung des ESD-Generators beträgt 2 kV. Im Bild 2 erkennt man weiterhin, dass die größte Spannungsinduktion vom ESD Einschwingvorgang erzeugt wird. Der nach Norm definierte 0,7 bis 1 ns Anstieg der Entladestromspitze erzeugt eine geringere Störspannungsinduktion (Bild 2, Kurven ohne Einschwingvorgang).

Der ESD Einschwingvorgang des ESD-Generators besitzt eine höhere Störwirkung als die Entladestromspitze. Die nach Norm definierten Kurvenformparameter eignen sich damit nicht zur umfassenden Beschreibung der Störwirkung des ESD-Generators. In der Praxis sind die Einschwingvorgänge stark vom Typ des ESD-Generators abhängig.

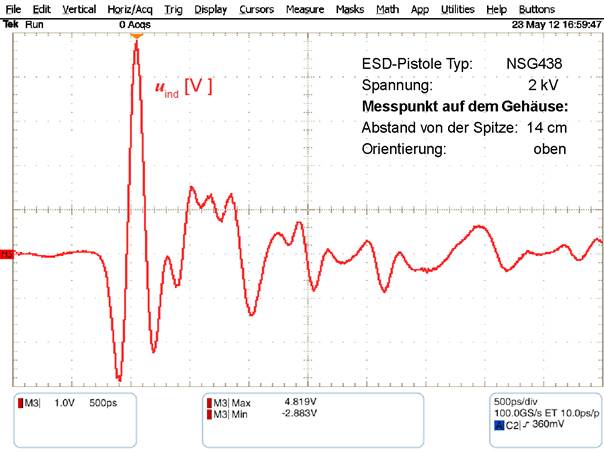

Eine zusätzliche Störwirkung des ESD-Generators werden durch die Felder B2 und B3 (Bild 1) ausgelöst. Die vom Feld B2 in einer 8 mm2 großen Leiterschleife erzeugte Störspannung ist in Bild 3 dargestellt. Der Spannungsverlauf weicht vollkommen vom üblichen Verlauf der bekannten ESD-Vorgänge ab. Die größte Störwirkung auf ICs besitzt der 200 ps breite Nadelimpuls. Er hat eine Amplitude von 4,8 V. Für langsame ICs der älteren Generation war dieser Impuls zu kurz. Er konnte kaum Störungen hervorrufen. Moderne schnelle ICs können diesen schmalen Impuls verarbeiten und werden gestört. Die Besonderheit ist, dass dieser Vorgang (durch das Feld B2 induzierte Spannung) nichts mit dem Normpuls zu tun hat. Er tritt zusätzlich zum eigentlichen Prüfvorgang auf. Dadurch ist die Normprüfung nicht mehr eindeutig.

Eine Induktionsschleife kann sich außerhalb des ICs auf der Flachbaugruppe oder im IC-Gehäuse befinden. Außerhalb wird sie durch einen Leiterzug gebildet, der sich hier zum Beispiel über einen niederohmigen Treiber zur Masse schließt. Durch den Leiterzug wird die Störspannung leitungsgebunden in den IC geleitet. Innerhalb des ICs wird die Induktionsschleife durch Pins, Lead Frame und Bonddraht gebildet. Die in der Induktionsschleife induzierte Spannung uind steht am Eingang des ICs an. Beide Spannungen – die äußere und die innere – wirken im Inneren des ICs störend. Die Spannung uind hängt von der Steilheit des Entladestroms, bzw. des Magnetfeldes des ESD-Generators ab. Dieser Zusammenhang wird mit dem Induktionsgesetz: uind = -d Φ / d t beschrieben. Je steiler der Störvorgang ist, umso höher ist die induzierte Spannung. Beim Burstgenerator IEC 64000-4-4 ist die Steilheit des Impulses 5 ns. Die Magnetfelder des Burstgenerators induzieren eine geringere Spannung als der Störvorgang des ESD-Generators. Der ESD-Generator besitzt eine Flankensteilheit von 0,7 bis 1 ns und wird bei gleichem Strom fünf Mal mehr Spannung induzieren. Die Einschwingvorgänge auf der Flanke des ESD-Generators besitzen eine Steilheit von ca. 200 ps. Diese Einschwingvorgänge werden eine noch höhere Spannung induzieren.

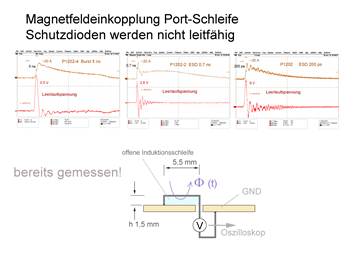

Dieser Zusammenhang ist im Bild 4 dargestellt. Der dargestellte Strom erzeugt ein Magnetfeld B, das die Leiterschleife durchsetzt. In der Leiterschleife wird die Spannung uind induziert. Die Störvorgänge: Burst, ESD, ESD Einschwingvorgang erzeugen unterschiedlich hohe Spannungsinduktionen. Die Breite des induzierten Spannungsimpulses entspricht der Anstiegszeit des Stromes. Bei Burst entstehen Impulse, die 5 ns breit sind. Bei ESD 1ns und beim ESD Einschwingvorgang entstehen Impulse von 200 ps Breite. Bei modernen ICs wird auch bei 200 ps breiten Impulsen der IC die Störung verarbeiten und dadurch gestört. Das kann bis zum Totalausfall des IC führen.

Die Höhe der induzierten Spannung ist nach dem Induktionsgesetz umgekehrt proportional zur Steilheit (Anstiegszeit) des Störvorgangs. Die Messungen für Bild 4 wurden mit definierten Feldquellen durchgeführt (Bild 5). Diese besitzen für die unterschiedlichen Störvorgänge eine feste Geometrie für die Felderzeugung. Dadurch wird der Prüfstrom immer die gleiche Feldverkopplung erzeugen. Damit werden die Messergebnisse für die drei beschriebenen Störvorgänge vergleichbar. Ein IC kann den definierten Feldern ausgesetzt werden und seine Störfestigkeit unter Funktion geprüft werden.

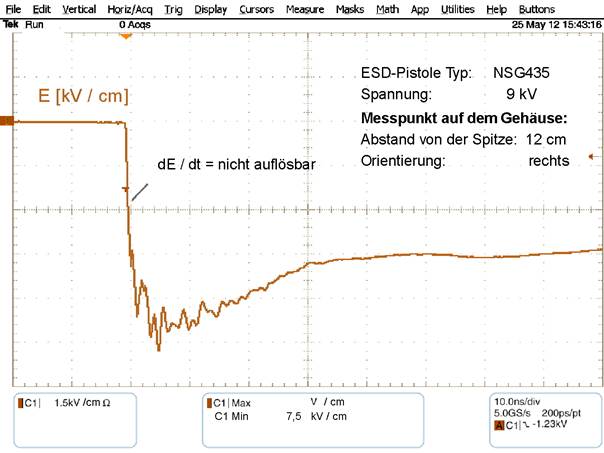

Im ESD-Generator werden beim Entladevorgang am Hochspannungsschalter, an Stromleitern und weiteren Bauteilen Schaltspannungen mit hoher Flankensteilheit entstehen (Bild 1). Diese Schaltspannungen erzeugen elektrische Felder hoher Flankensteilheit, die aus dem Generatorgehäuse auf den Prüfling auskoppeln. Im Bild 6 ist das elektrische Feld dargestellt, dass im hinteren Bereich aus dem Gehäuse eines ESD-Generators austritt. Die Flankensteilheit ist ca 1 ns.

Elektrisches Feld koppelt z.B. in eine hochohmige Signalleitung ein (Schaltkreiseingang). Die betroffene Signalleitung besitzt eine geringe kapazitive Kopplung zum ESD-Generator. Die Größe dieser Kapazität ist von der Fläche der Signalleitung abhängig. Die Kapazität dieser Kopplung liegt im fF-Bereich. Das elektrische Feld des ESD-Generators treibt einen kapazitiven Strom in die Signalleitung. Dieser Strom fließt über den Pull up Widerstand oder den Innenwiderstand des angeschlossenen Treibers gegen Masse (GND). Am Widerstand entsteht durch den Strom ein Spannungsimpuls. Dieser Spannungsimpuls gelangt an den Eingang des ICs und beeinflusst den IC. Der Scheitelwert des Spannungsimpulses ist abhängig von der Flankensteilheit des elektrischen Feldes, dem Pull up Widerstrand und der dem Feld ausgesetzten Oberfläche der Signalleitung. Die Impulsbreite ist abhängig von der Anstiegszeit. Je steiler der Störvorgang ist, umso höher ist die eingekoppelte Spannung. Beim Burstgenerator IEC 64000-4-4 ist die Steilheit des Impulses 5 ns. Die E-Felder des Burstvorgangs koppeln eine geringere Spannung als der Störvorgang des ESD-Generators. Der ESD-Generator besitzt eine Flankensteilheit von 0,7 bis 1 ns und wird fünf Mal mehr Spannung einkoppeln. Die steilsten E-Felder eines ESD-Generators liegen bei 200 ps. Diese Vorgänge werden eine noch höhere Spannung einkoppeln.

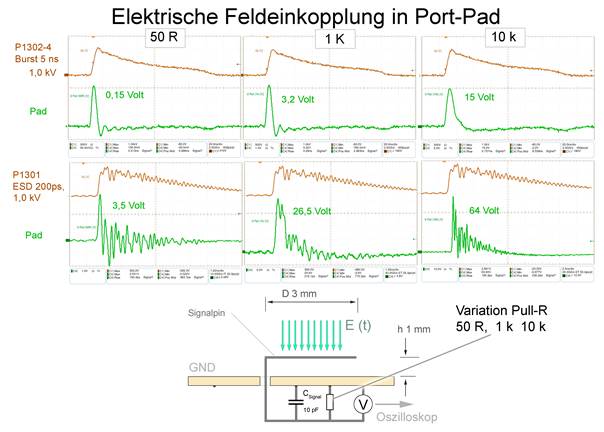

Diese elektrische Einkopplung wurde experimentell untersucht. Es wird ein ähnlicher Versuchsaufbau wie in Bild 5 verwendet. Als Feldquelle dient eine E-Feldquelle. Im Bild 7 sind die Ergebnisse dargestellt. Für die Messung wurde ein 5 ns Burst Impuls und ein 200 ps ESD Impuls verwendet. Des Weiteren wurde die Abhängigkeit vom verwendeten Pull up Widerstand (Treiber) untersucht.

Die eingekoppelte Spannung ist der Größe des Pull up Widerstandes proportional. Die geringste in den IC eingekoppelte Spannung (0,15 V) wird bei 5 ns Flanke und 50 Ohm Pull up Widerstand erzielt. Diese Spannung wird im IC noch keine Beeinflussung hervorrufen. Die größte Spannung entsteht bei einer 200 ps Flanke und einem Pull up Widerstand von 10 kOhm. Sie beträgt 64 V. Aus dem Bild 7 ist zu erkennen, dass der 200 ps Impuls bereits bei einem niederohmigen Pull up (Treiber) Widerstand von 50 Ohm Störungen im IC hervorrufen kann (3,5 V). Das macht diesen Impuls für elektronische Schaltungen besonders gefährlich. Denn kleinste Abschnitte von niederohmig getriebenen Leitungen, wie Datenbus, Adressbus, können über diesen Weg beeinflusst werden. Es genügt die Oberfläche von der Größe eines Testpunkts an der entsprechenden Leitung, um den IC zu stören. Dieses Problem tritt nur bei modernen hoch integrierten ICs auf, die die entsprechende Schnelligkeit besitzen, diesen Impuls zu verarbeiten.

Für die Entwicklung einer Baugruppe mit hoch integrierten ICs ist es wichtig, die Störfestigkeit des verwendeten ICs zu kennen. An einem IC sind durchaus nicht alle Pins gleich empfindlich. Es gibt meist nur einige hochempfindliche Pins. Diese Pins gilt es zu ermitteln, um an diesen zielführend entsprechende EMV-Gegenmaßnahmen anzuwenden.

Um zum Beispiel die Beeinflussung durch elektrisches Feld zu reduzieren, ist es erforderlich die Signalleitungen in die Innenalgen zu legen und mit GND-Flächen beidseitig zu schirmen. Zu beachten ist, dass Testpunkte oder Vias ebenfalls reduziert werden müssen.

Zur Ermittlung der leitungs- oder feldgebundenen Störfestigkeit von ICs stehen moderne Messverfahren und Testgeräte zur Verfügung.