Vom Gerätetest zum IC-Testsystem Teil 1

Einleitung

Die Einhaltung der EMV-Anforderungen wird immer anspruchsvoller. Die besondere Herausforderung, die mit dem Technischen Fortschritt aus der Verringerung der Strukturbreite entsteht ist die Beherrschung der Störfestigkeit.

Durch die erhöhten Anforderungen an die Störfestigkeit werden erhebliche zusätzliche Kosten bei der Geräteentwicklung und bei den Herstellungskosten der Geräte verursacht. Gegensteuern kann man, indem man schon auf Bauteilniveau, also für ASICs und ICs entsprechende Störfestigkeitstests durchführt. Mit den Ergebnissen der Störfestigkeitstests kann eine Vorselektion der ICs und ASICs für die Baugruppenentwicklung getroffen werden. Des Weiteren können die aus den Störfestigkeitstests resultierenden Erkenntnisse in die IC- und ASIC-Entwicklung einfließen und zur Optimierung der Bauteile beitragen.

In der Industrie werden bereits Testverfahren angewendet, die weitreichende Erfahrungen zur Beurteilung der Störfestigkeit von ICs und ASICs erbracht haben.

Das Konzept des Testverfahrens besteht darin, dass direkt an den Pins des zu testenden ICs Störimpulse angelegt werden. Die Form und Amplitude der Störpulse sind so gewählt, dass diese den Störbeeinflussungen entsprechen, die typischerweise direkt an Pins von ICs anstehen würden, wenn ein Gerät, dass diesen IC enthält, einem genormten Störfestigkeitstest unterzogen würde oder sich in gestörter Umgebung befindet.

Technische Ausrüstungen, Anlagen und Geräte werden im Betrieb hauptsächlich von pulsförmigen Störsignalen beaufschlagt. Entsprechend bilden die genormten Gerätetests beispielsweise die Funkenbildung an Schaltkontakten (Burst) oder elektrostatische Entladung (ESD) nach.

Betrachtet wird dabei die Störfestigkeit im aktiven Betrieb, also das Verhalten von spannungsversorgten ICs, die ihre Funktion ausführen. Das Kriterium für das Bestehen des Tests ist die ungestörte Funktion.

Weiterhin ist von Bedeutung, dass infolge von Gerätetest oder Umgebungseinfluss an den ICs Spannungen und in deren Folge Ströme auftreten, die deutlich über den spezifizierten Maximalwerten der ICs liegen.

Die Untersuchung der Störfestigkeit auf IC-Niveau hat den Vorteil, dass die Einflüsse des Gerätedesigns auf die EMV, beispielsweise die Gestaltung des Leiterplattenlayouts, die Art und Belegung der Steckverbinder oder die Gehäusekonstruktion nicht betrachtet werden müssen. Auch sind bei direkten IC- Störfestigkeitstests die parasitären Effekte weniger ausgeprägt als bei einem Gerätetest. Daraus ergibt sich eine bessere Reproduzierbarkeit der Testergebnisse.

Es gibt ein Testsystem zur Untersuchung der Störfestigkeit von ICs. Das Testsystem ist ausführlich beschrieben in /1/.

Die vorliegende Schrift soll den Zusammenhang zwischen Gerätetest und Pin-granularem IC-Test nachweisen.

Gerätetests

Die Durchführung von Störfestigkeitstests mit pulsförmigen Störgrößen hat die größte Bedeutung in technischen Anlagen und Geräten. Der Grund dafür ist, dass die Prüflinge in ihrem Einsatzgebiet ebenfalls pulsförmigen Störgrößen ausgesetzt sind. Die zunehmende Digitalisierung und die Zunahme elektronischer Produkte in allen Bereichen des Lebens erfordern eine hohe Robustheit hinsichtlich der Störfestigkeit der Geräte.

Die Störpulse der relevanten Gerätetests für die Störfestigkeit (Burst- und ESD-Test) werden in den folgenden Normen beschrieben:

| IEC 61000-4-4 | fast transient immunity test (burst) |

|---|---|

| |

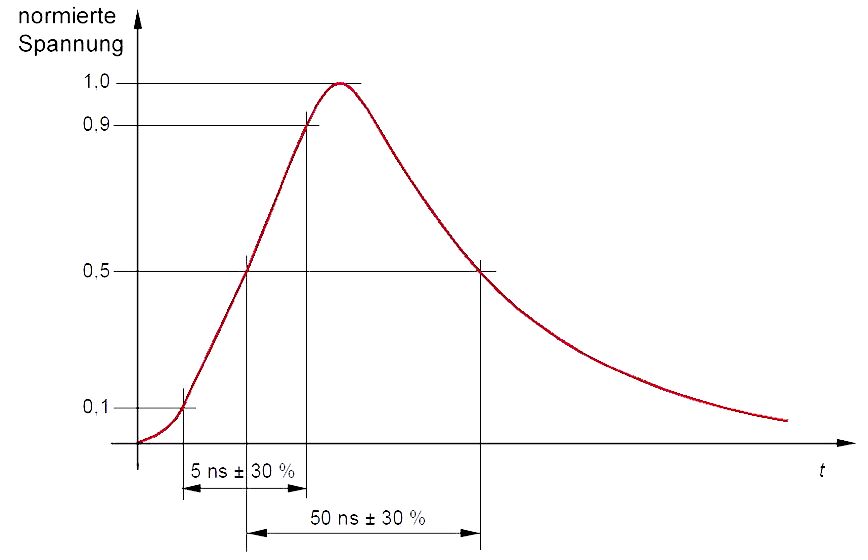

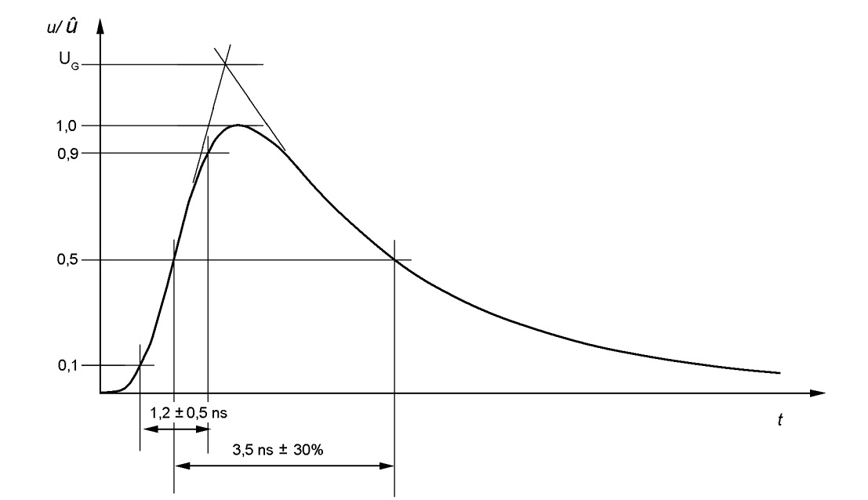

| Bild 1 Zeitlicher Verlauf eines Burstimpulses nach IEC 61000-4-4 | |

Aus einem Quellwiderstand von 50 Ohm werden Pulse von mindestens ±2 kV mit 5 ns Vorderflanke und 50 ns Rückflanke (halbe Amplitude) an das Gerät angelegt (Bild 1). Aus diesen Pulsen setzen sich Burst-Pakete zusammen.

| IEC 61000-4-2 | electrostatic discharge immunity test (ESD) |

|---|---|

| |

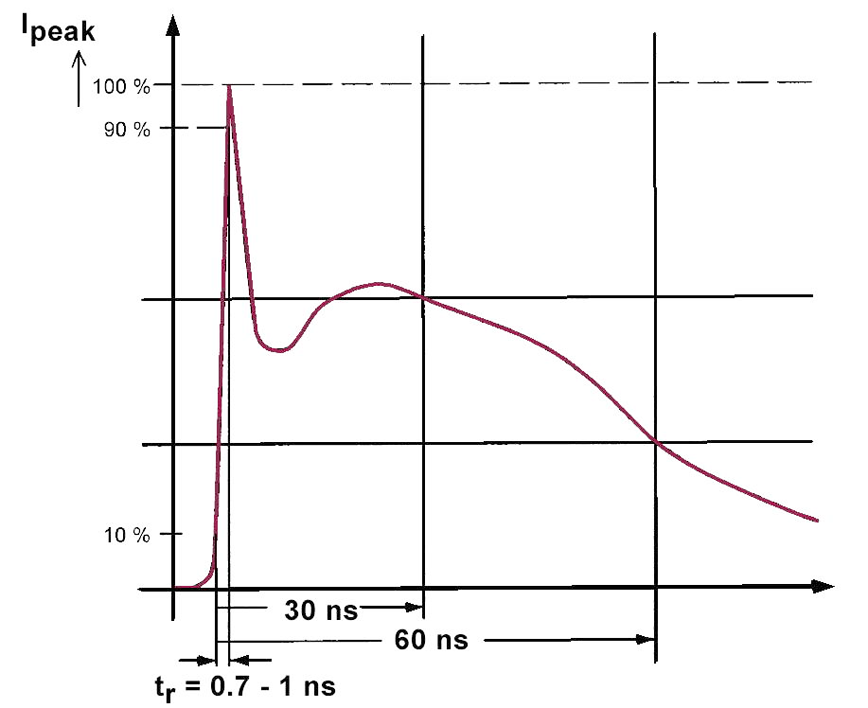

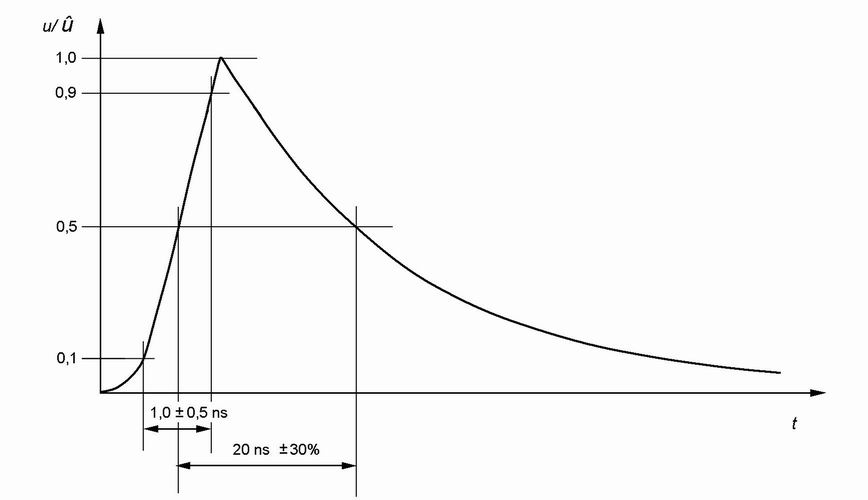

| Bild 2 Zeitlicher Verlauf eines ESD-Impulses nach IEC 61000-4-2 | |

Aus einem Quellwiderstand von 330 Ohm werden Pulse von mindestens ±6 kV mit 0,7 ns Vorderflanke und 5 ns Rückflanke (halbe Amplitude) an das Gerät angelegt (Bild 2).

Prinzipielle Wirkung der Störungen beim Gerätetest

Ein Gerät wird zum Nachweis der Störfestigkeit oder auch im bestimmungsgemäßen Einsatz mit pulsförmigen Störgrößen beaufschlagt. Dabei gibt es zwei grundsätzliche Wirkmechanismen, die im Folgenden einzeln betrachtet werden, die jedoch gleichzeitig auftreten.

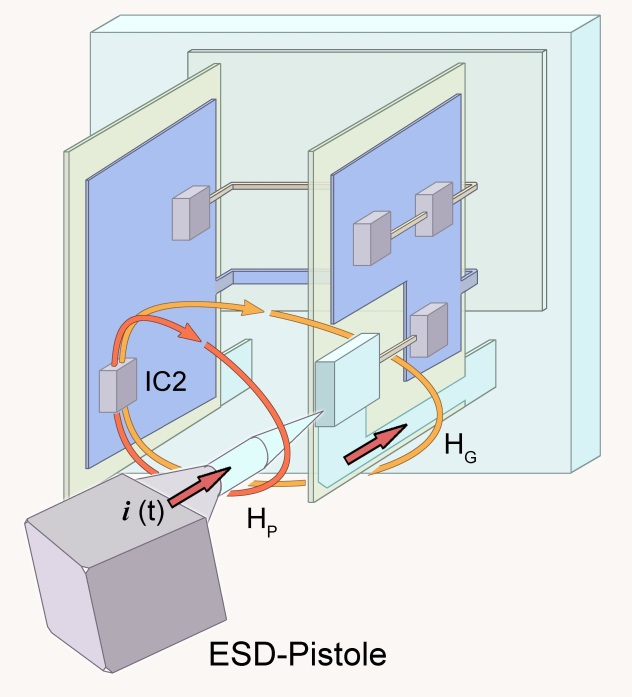

1. Magnetfeld-Kopplung

Der am Gerät anliegende primäre Störimpuls (ESD-Puls oder Burst) der Spannung u(t) bewirkt einen durch das Gerät fließenden Störstrompuls i(t) (Bild 3). Um den vom Störstrom i(t) durchflossenen Leiter bildet sich das Störmagnetfeld H(t). Je geringer die Impedanz im Primärkreis ist, umso höher ist der Stromfluss und damit das H-Feld.Die Feldstärke ergibt sich im Idealfall für den geraden Leiter aus (r Abstand).

| [1] |  |

Das Störmagnetfeld durchdringt das Gerät und die darin befindlichen Leiterkarten und Bauteile. Auf den Leiterkarten oder in den Bauteilen (z.B. IC, Bild 3) befinden sich Leiterschleifen in denen das Störmagnetfeld über die Induktivität L eine sekundäre Störspannung u_sec(t) induziert.

| [2] |  |

Diese Störspannung liegt nun beispielsweise an einem IC-Pin oder in einem IC an und kann im IC zum Fehlverhalten führen.

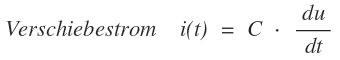

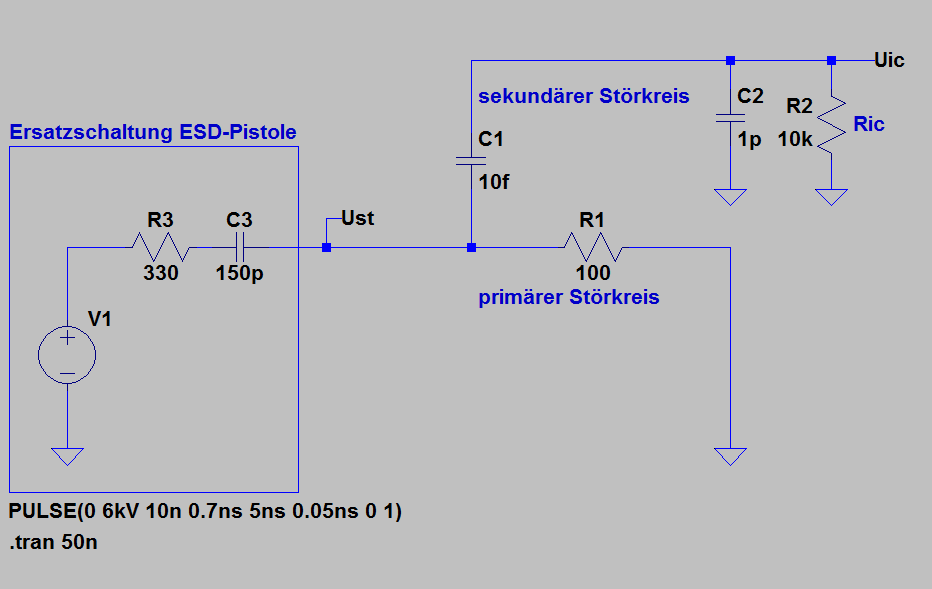

2. E-Feld-Kopplung

Der am Gerät anliegende primäre Störimpuls (ESD-Puls oder Burst) der Spannung u(t) bewirkt im Gerät einen Spannungsabfall über die Baugruppe (Bild 4). Aus der Spannungsdifferenz entlang der betrachteten Geometrie ergibt sich ein elektrisches Feld E(t). Je höherimpedant der primäre Strompfad ist, umso höher ist die Spannungsdifferenz und damit das entstehende E-Feld. Das Feld überträgt die Störung über kapazitive Kopplung als Verschiebestrom i(t) in sekundäre Schleifen wie Signalleitungen / IC-Pins.

Dieser Vorgang lässt sich durch eine Koppelkapazität C, die im fF-Bereich liegt, beschreiben [3]. Am Innenwiderstand der sekundären Schleife entsteht durch den kapazitiv eingekoppelten Strom i(t) eine Störspannung. Diese Störspannung kann an einem IC-Pin anliegen und eine Beeinflussung im IC auslösen.

| [3] |  |

In beiden Fällen (durch Magnetfeld und E-Feld verursachte Kopplung) wird beim Übergang vom primären Störkreis in den sekundären Wirkungskreis die Störgröße um einen Faktor (Gerätefaktor) verringert und liegt an der aktiven Elektronik (z.B. am IC) an. Die bei einem ESD-Gerätetest üblichen Störspannungen von 6 kV reduzieren sich abhängig von der Impedanz im primären und im sekundären Störkreis auf eine Spannung im Bereich von …0,1 V bis mehrere 100 V.

Auf der Leiterplatte bestückte ICs sind den störungsgetriebenen Magnetfeldern H(t) und E-Feldern E(t) ausgesetzt.

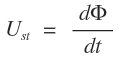

Magnetfeldeinkopplung in ICs

Die magnetische Flussdichte Bst(t) durchdringt kleinste Leiterschleifen beispielsweise zwischen einem IC und einem angeschlossenen Stütz-Kondensator (Bild 5). In der Leiterschleife wird durch den magnetischen Fluss Φ eine Spannung Ust induziert [5].

| [4] |  |

| [5] |  |

Die Spannung Ust treibt einen Störstrom in den IC hinein. Die Impedanz dieser Störquelle ist, bedingt durch die Entstehung in der Leiterschleife, niedrig. Das kann zu hohen Strömen Ist(t) führen.

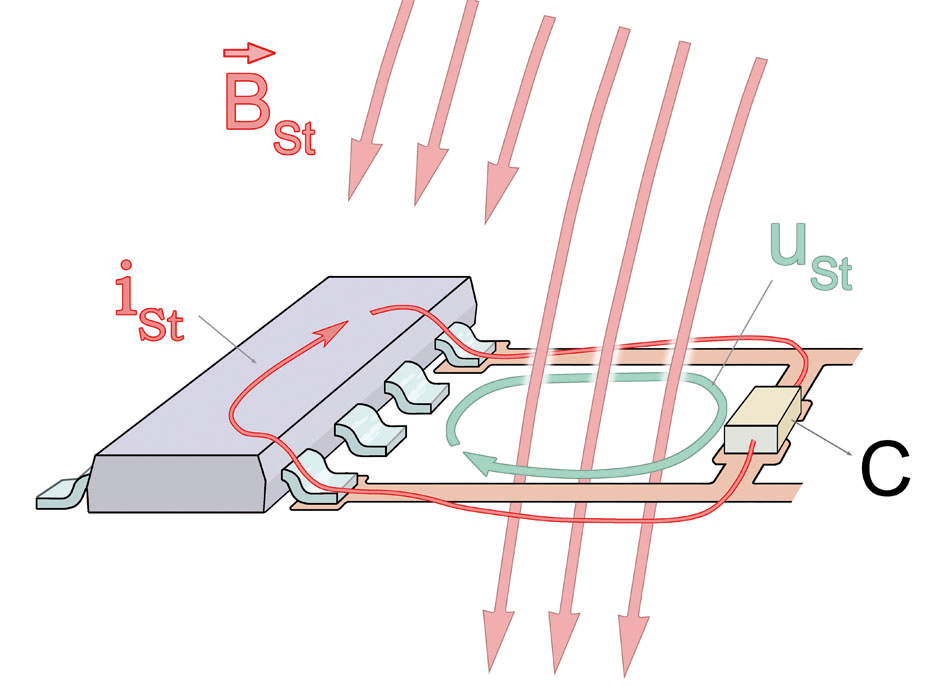

E-Feldeinkopplung in ICs

Die elektrische Feldstärke E(t) bzw. der auf die Leiterfläche bezogene Verschiebestrom D(t) (Bild 6) erzeugt im Leiter einen Störstrom Ist(t). Er bewirkt auf der Leiterfläche eine Spannungsanhebung Ust(t). Diese Spannungsanhebung kann logische Signale, die auf der Leitung übertragen werden, verfälschen. Der Verschiebestrom Ist(t) kann auch in ICs einfließen und weitere Störvorgänge auslösen. Die Störquelle „Elektrisches Feld“ besitzt eine hohe Impedanz.

Simulation

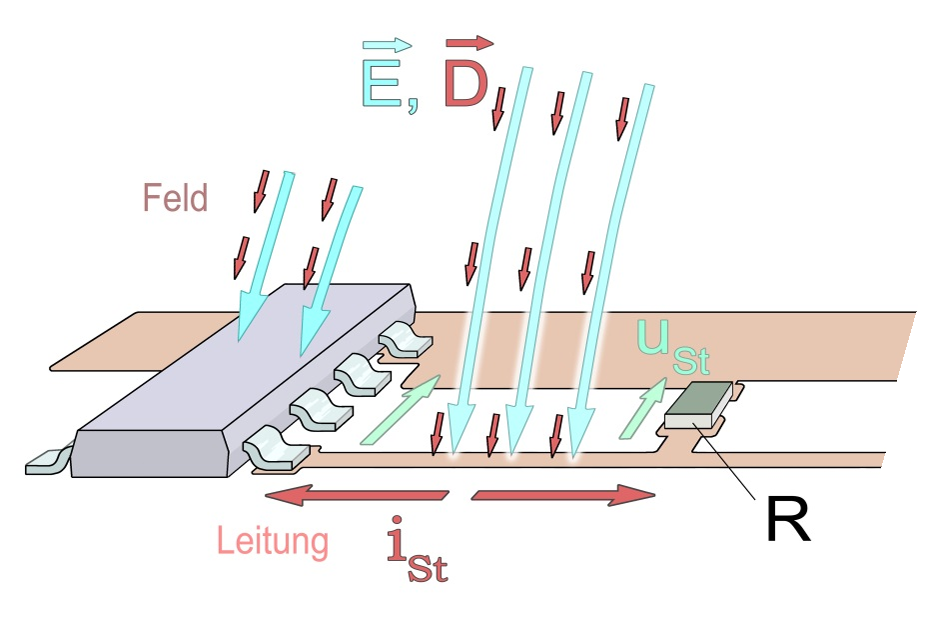

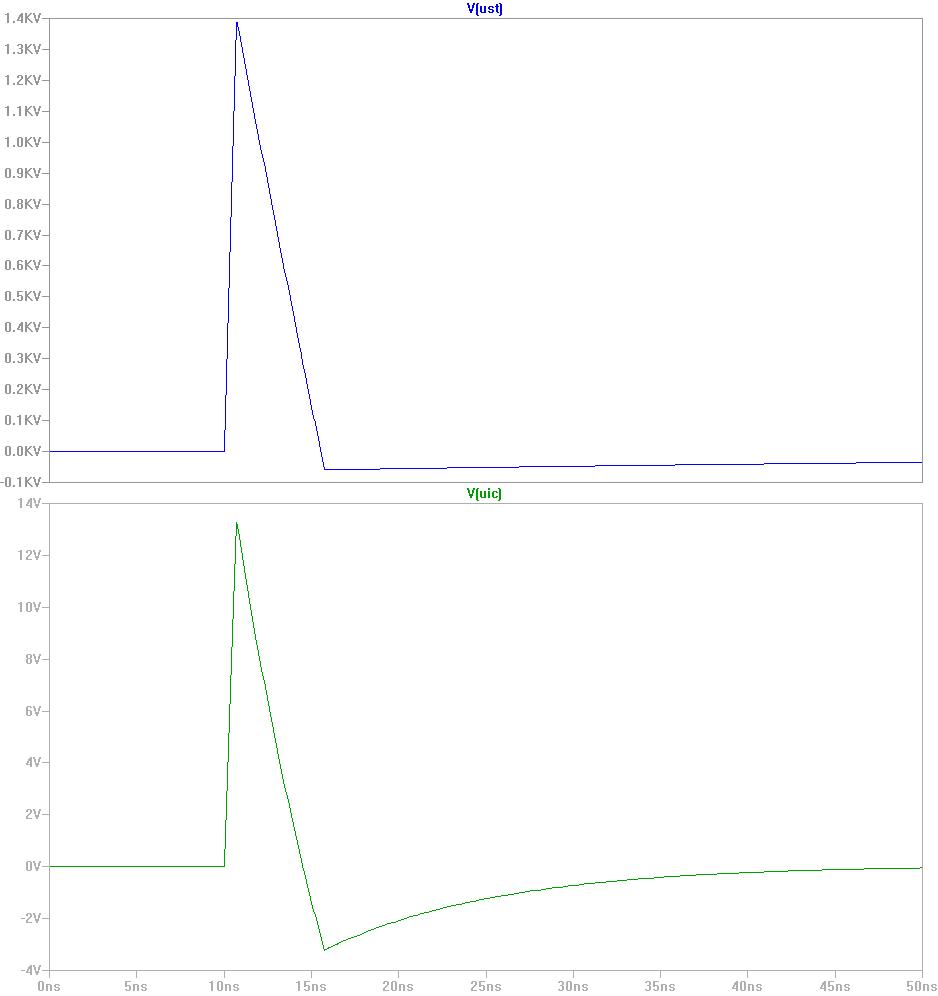

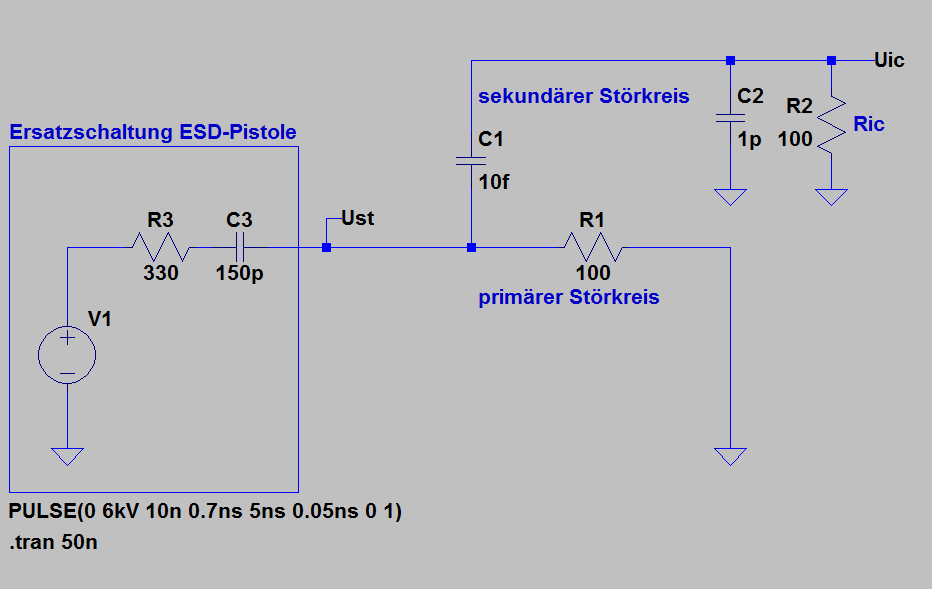

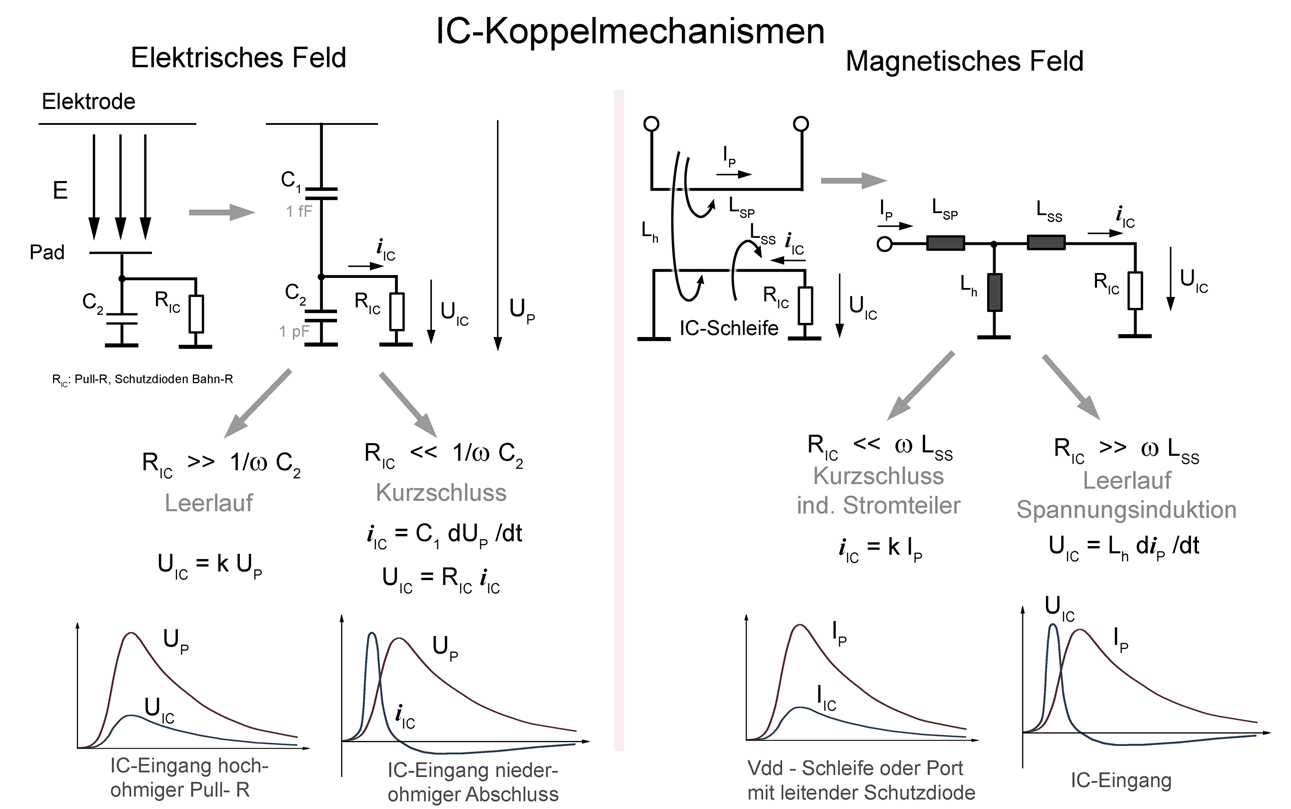

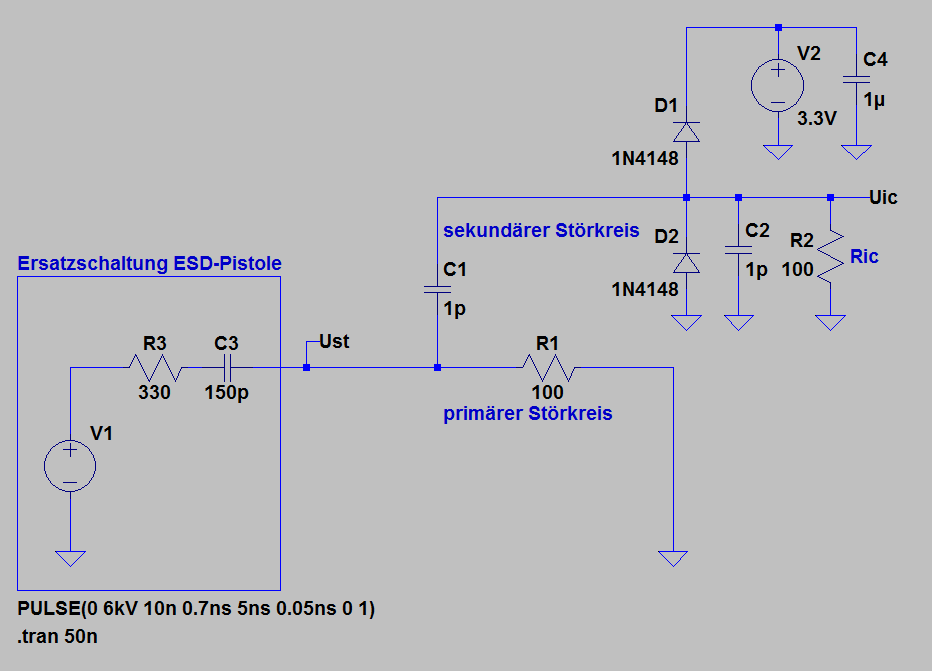

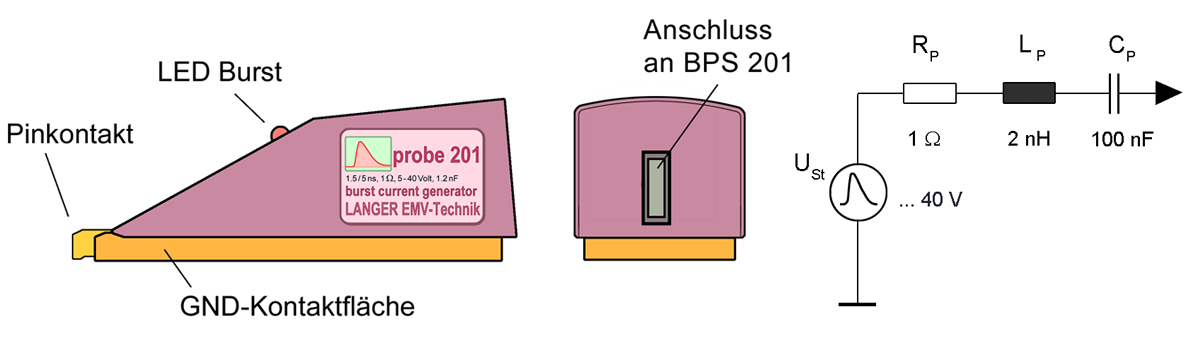

Die folgenden Simulationen (Bild 7 bis Bild 12) zeigen die prinzipiellen Verhältnisse. Im Bild 7 ist die Erzeugung des ESD-Pulses stark vereinfacht realisiert. Die Ersatzschaltung basiert auf Bild 4.

Abschätzung der Störspannung am IC

Es wird ein positiver Störpuls der Amplitude 6 kV als Kontaktentladung in den primären Störkreis eingespeist (Bild 7). An der primären Impedanz R1 (Ableitweg Bild 4) entsteht eine Störspannungsspitze Ust von 1,4 kV. Durch kapazitive Kopplung (Elektrisches Feld) über C1 liegen an einem hochohmigen IC-Pin immer noch 13,5 V Störspannung an. Die Impedanz des primären Störkreises kann deutlich größer sein (1 kOhm), so dass Störspannungen am IC-Pin den Wert von 100 V überschreiten können. Damit werden die im Datenblatt angegebenen Maximum Ratings von ICs deutlich überschritten.

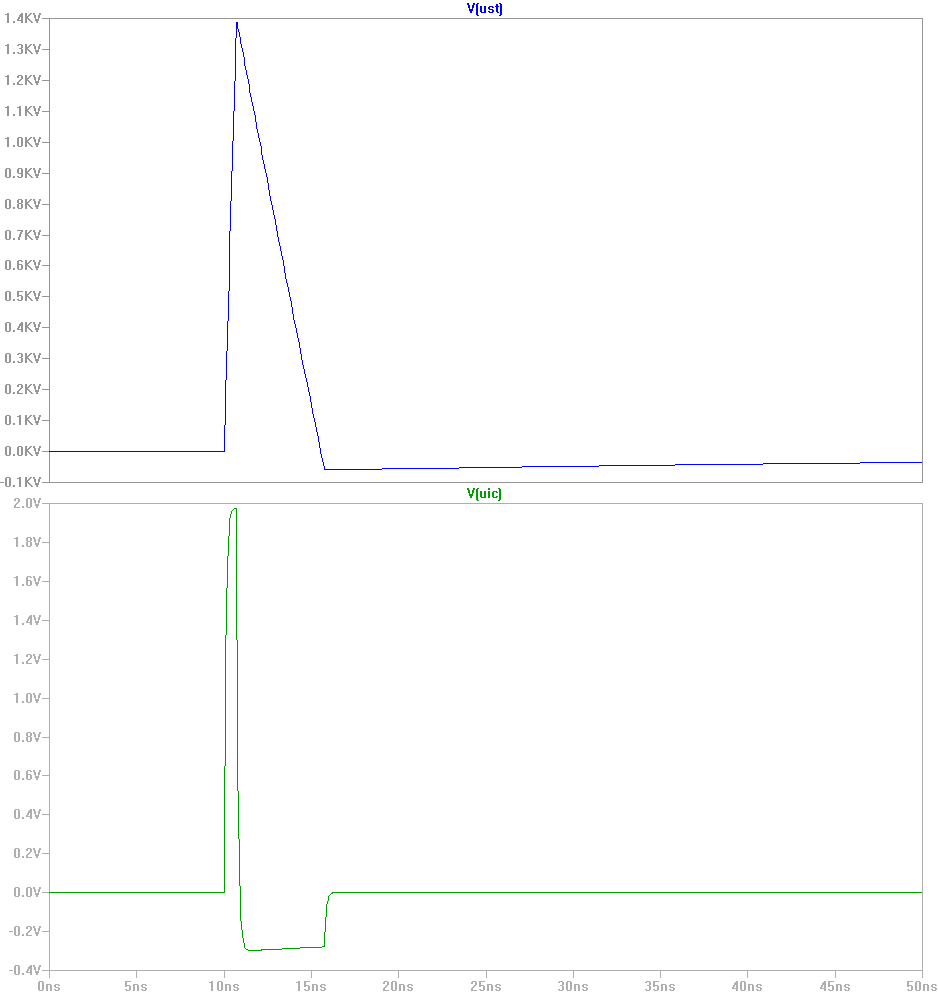

Kopplungsarten

Die Art der Kopplung ist weiterhin abhängig vom Verhältnis der Quellimpedanz zur Lastimpedanz, d.h. zur Eingangsimpedanz des ICs.

E-Feldkopplung:

Bei einer Flankensteilheit von 1 ns ergibt sich eine Übertragungsfrequenz von max. 1 GHz. Vorerst wird angenommen, dass die Koppelkapazität C1 1 pF ist. Sie hat dann eine Impedanz X von 159 Ohm. Wenn der Eingangswiderstand des ICs bei 10 kOhm liegt, ist er viel größer als der Quellwiderstand (Impedanz von C1). Die Folge davon ist, dass der an R2 (am IC) anliegende Störpuls die gleiche Kurvenform hat wie der primäre Störpuls. Es ergibt sich eine proportionale Spannungsteilung mit dem kapazitiven Teiler C1, C2.

Ri des IC ≫ XC1

Völlig andere Verhältnisse ergeben sich, wenn die Lastimpedanz geringer ist als die Quellimpedanz. Im folgenden Beispiel ist R2 = 100 Ohm, C1 = 10 fF.

Ri des IC < XC1

Unter diesen Bedingungen liegt der primäre Störpuls differenziert am IC an (Bild 9, Bild 10).

H-Feld-Kopplung

Bei der H-Feld Kopplung sind die Verhältnisse genau umgekehrt. Bei Leerlauf

Ric ≫ Xss wird differenziert,

ist Ric < Xss wird stromgeteilt.

Die Zusammenfassung der Koppelmechanismen sind im Bild 11 dargestellt. Bei der H-Feld-Kopplung wird das Trafoersatzschaltbild mit Hauptinduktivität (Lh) und Streuinduktivität (Ls) zugrunde gelegt.

Literatur Teil 1:

| /1/ | "Richtlinie EMV-Anforderungen und Prüfverfahren zum Test der Pulsstörfestigkeit von ICs und ASICs" Langer EMV-Technik GmbH |

Vom Gerätetest zum IC-Testsystem Teil 2

Wirkung im IC

Zur Vermeidung der Zerstörung der empfindlichen Strukturen in ICs durch Überspannungen werden Schutzmechanismen mit integriert. Beim Design dieser Schutzeinrichtungen geht man heute ausschließlich davon aus, dass der zu schützende IC nicht mit Betriebsspannung versorgt ist, sich also nicht in Funktion befindet. Damit ist der IC vor zu hohen elektrostatischen Spannungen geschützt, die bei der Herstellung beim Transport und bei der Verarbeitung in der Elektronikfertigung auftreten.

Im Gegensatz dazu werden bei den beschriebenen Gerätetests die ICs an Versorgungsspannung und in Funktion betrieben. Schutzschaltungen können im praktischen Betrieb (IC versorgt) unter Störeinfluss unbeabsichtigt innere Kurzschlüsse hervorrufen.

Die in die ICs integrierten Schutzstrukturen werden in der Regel vom IC-Hersteller nicht veröffentlicht. Vereinfacht kann man davon ausgehen, dass die folgenden Mechanismen wirken:

- Überspannung an Versorgungsanschlüssen wird durch Strukturen begrenzt, die funktionell Z-Dioden entsprechen

- an Ein- und Ausgängen erfolgt die Begrenzung von Überspannungen durch Dioden- oder Transistorstrukturen gegen die Versorgungsspannungsanschlüsse

Abhängig vom zu testenden IC-Pin sind die Lastimpedanzen unterschiedlich. An Stromversorgungsanschlüssen kann man von einer niedrigen Lastimpedanz ausgehen. Hier wird ein kapazitiv eingekoppeltes Signal wie oben beschrieben differenziert. Wird das Signal induktiv eingekoppelt, erfolgt eine Spannungsteilung.

An IC-Eingängen ist die Impedanz relativ hoch, solange man im spezifizierten Pegelbereich bleibt. Wird die Begrenzungsspannung der Schutzschaltung überschritten, kommt es über die Schutzschaltungen und die Stromversorgung zur drastischen Reduzierung der Impedanz, bedingt durch das kapazitiv überbrückte Versorgungssystem. Somit ergibt sich eine Kombination aus spannungsteilendem Verhalten und Differenzieren in Kombination mit der spannungsbegrenzenden Wirkung der Schutzelemente. Beim Einfließen von Störstrom über die Schutzschaltungen in den IC können innere Funktionsfehler ausgelöst werden.

Je nach Eigenschaften der Dioden (hier langsame Si-Dioden) treten unterschiedliche Kurvenverläufe auf. Erkennbar ist der erhebliche Störstrom (I(D1)) von 2 A, der über die Dioden in das Stromversorgungsystem fliesst. Man muss bedenken, dass diese Situation beim Gerätetest (nach IEC 61000-4-2 ESD) eintritt, aber auch in der normalen Applikation eines ICs, wenn es zu einer elektrostatischen Entladung kommt.

Erforderliche Pulsbreite für den IC-Test

Ziel der Definition eines Prüfpulses für den Störfestigkeitstest von ICs ist es, ein möglichst breites Spektrum von ICs mit unterschiedlicher Strukturbreite reproduzierbar testen zu können.

Strukturbreitenabhängig ändert sich die interne Verarbeitungsgeschwindigkeit eines ICs. Ein in grober Struktur gefertigter IC wird gegenüber Störereignissen eine gewisse Trägheit aufweisen.

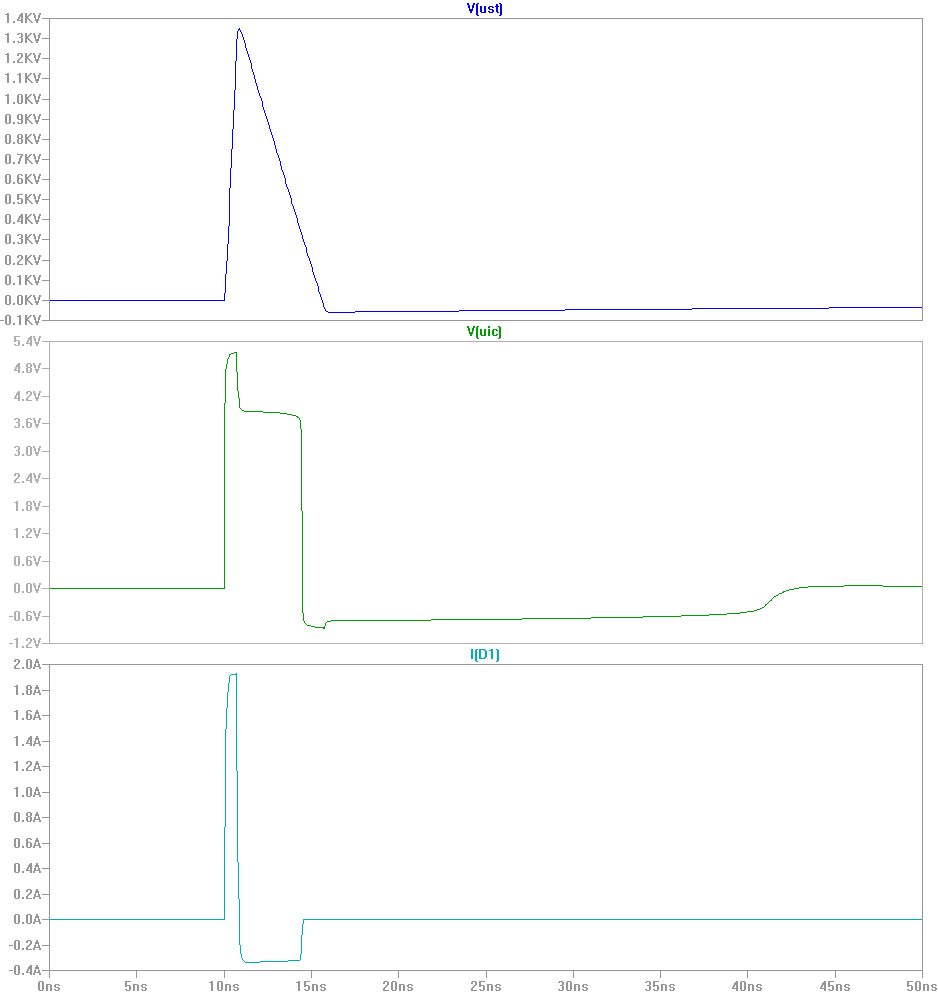

Zur Beurteilung der ICs kann die dynamische Schaltschwelle / Störschwelle zu Grunde gelegt werden. Im Bild 3 ist auf der X-Achse die Pulsbreite T des Störpulses, auf der Y-Achse die Störschwelle dargestellt. Für breite Pulse, im Bild 3 > 1,5 ns, ist die Störschwelle nahezu konstant (statische Störschwelle). Für kurze Pulse, im Bild 3 < 1,5 ns, steigt die Störschwelle an, der IC wird unempfindlich (dynamische Störschwelle). Die Grenze des Übergangs statisch / dynamisch ist abhängig von der Strukturbreite.

Bei Störungen über Stromversorgungssysteme sind zusätzlich weitere Verhaltensweisen zu beachten. Aus Bild 3 ist ableitbar, dass die Pulsbreite der Testgeneratoren für den IC-Test > 1,5 ns sein muss. Aufgrund der Technologieabhängigkeit ist diese Grenze fließend, so das Pulsbreiten von < 1,5 ns für entsprechend schnelle ICs möglich sind.

Notwendig für reproduzierbare Testergebnisse ist, die Pulsbreite für IC-Tests so zu wählen, dass man sicher im linearen Bereich, also in den Bereich der statischen Störschwelle liegt.

Mit zunehmendem technologischem Fortschritt verringern sich die Strukturbreiten und der Übergang vom statischen zum dynamischen Bereich verschiebt sich in Richtung kürzerer Pulsbreiten. [Vor 20 Jahren war ein IC mit Störpulsen von 2 ns Breite nicht sicher störbar.]

Folglich lassen sich die heute im statischen Bereich liegenden Testimpulse auch für ICs zukünftiger schnellerer Technologien verwenden.

Umgekehrt muss man allerdings feststellen, dass sich ICs mit kleineren Strukturen aufgrund niedrigerer Versorgungsspannung niedrigere Störschwellen besitzen, so dass technologiebedingt die Empfindlichkeit zunimmt. Die Bedeutung der Störfestigkeitstests wird damit in der Zukunft ebenfalls steigen.

Die IC-Testmethode

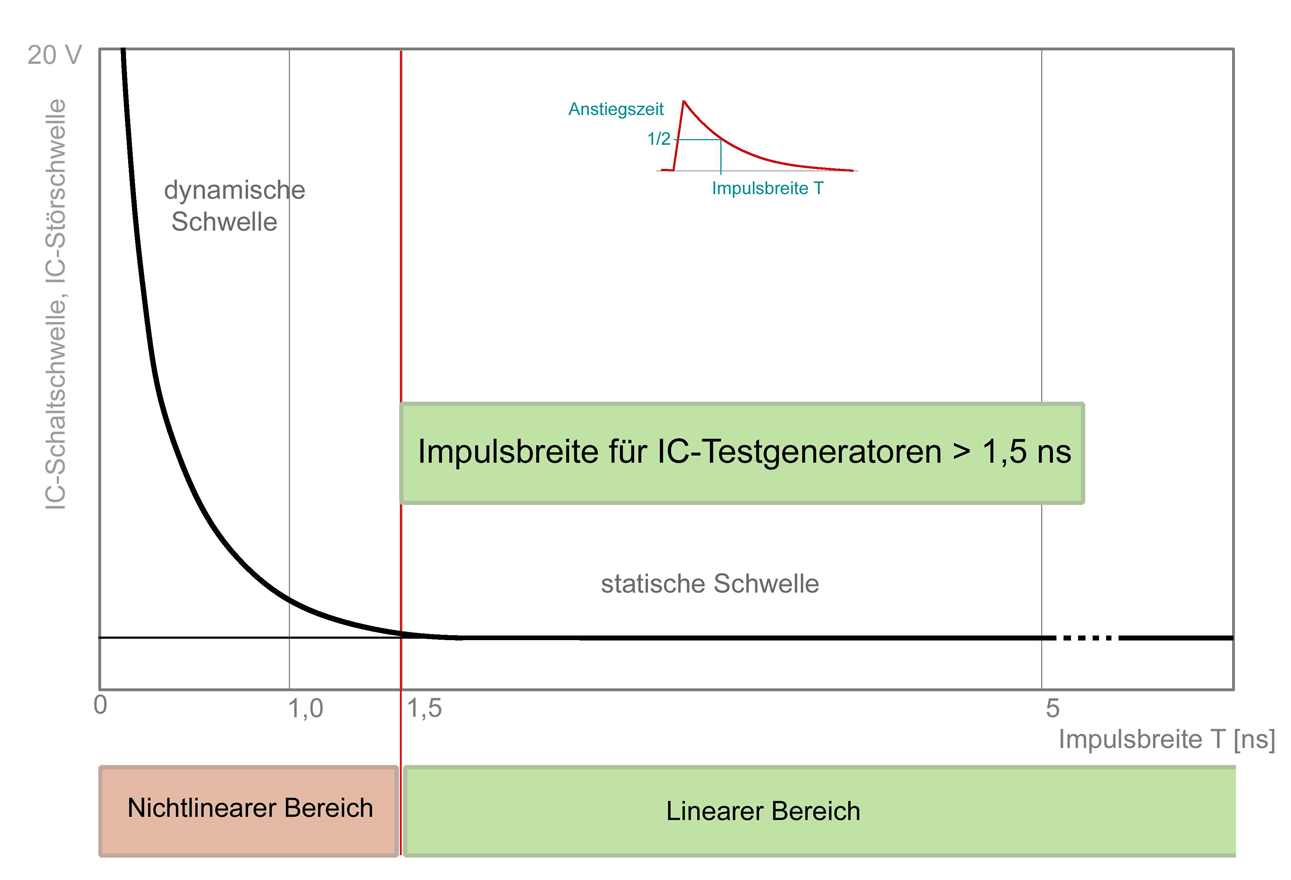

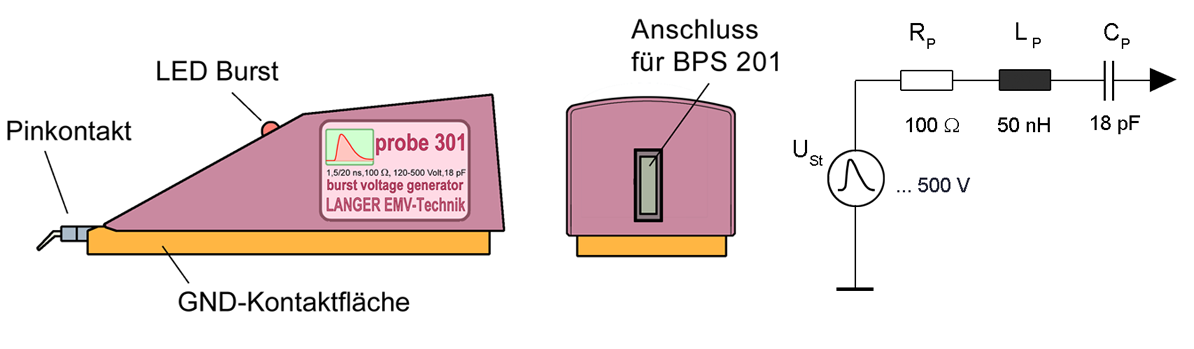

Entsprechend den Vorbetrachtungen sollten Pulsquellen mit niedriger und mit hoher Impedanz zur Verfügung stehen. Nachfolgend sind Ersatzschaltungen, Flankensteilheiten sowie die maximalen Spannungshöhen angegeben.

Die Pulsquelle mit niedriger Impedanz (Probe P2xx) ist ursächlich für den Test von Versorgungsanschlüssen vorgesehen. Dazu wird der Stütz-Kondensator in der zu prüfenden Schaltung entfernt. Er wird durch den Kondensator CP der sich in der Probe befindet ersetzt.

Pulsquelle mit niedriger Impedanz (Low-Impedance-Probe P2xx)

| RP = 1 Ohm |

| LP ≤ 2 nH |

| CP ≥ 100 nF |

| Spannungen bis ca. ± 40 V |

Pulsquelle mit hoher Impedanz (High-Impedance-Probe P3xx)

| RP = 100 Ohm |

| LP ≤ 50 nH |

| CP = 18 pF |

| Spannungen bis ca. ± 500 V |

Bei der Probe P2xx liegt die Pulsbreite, gebildet aus Vorder- und Rückflanke mit 1,2 ns / 3,5 ns im Bereich der statischen Störschwelle. Bei der Probe P3xx liegt die Pulsbreite, gebildet aus Vorder- und Rückflanke mit 1 ns / 20 ns im Bereich der statischen Störschwelle. Im Kurzschlussfall verringert sich die Pulsbreite der Probe P3xx auf 2 ns. Das geschieht beim leitfähig werden von Schutzschaltungen im IC. Damit liegt die Pulsbreite ebenfalls im Bereich der statischen Störschwelle. Durch interne Einschwingvorgänge verbreitert sich der Störpuls weiter.

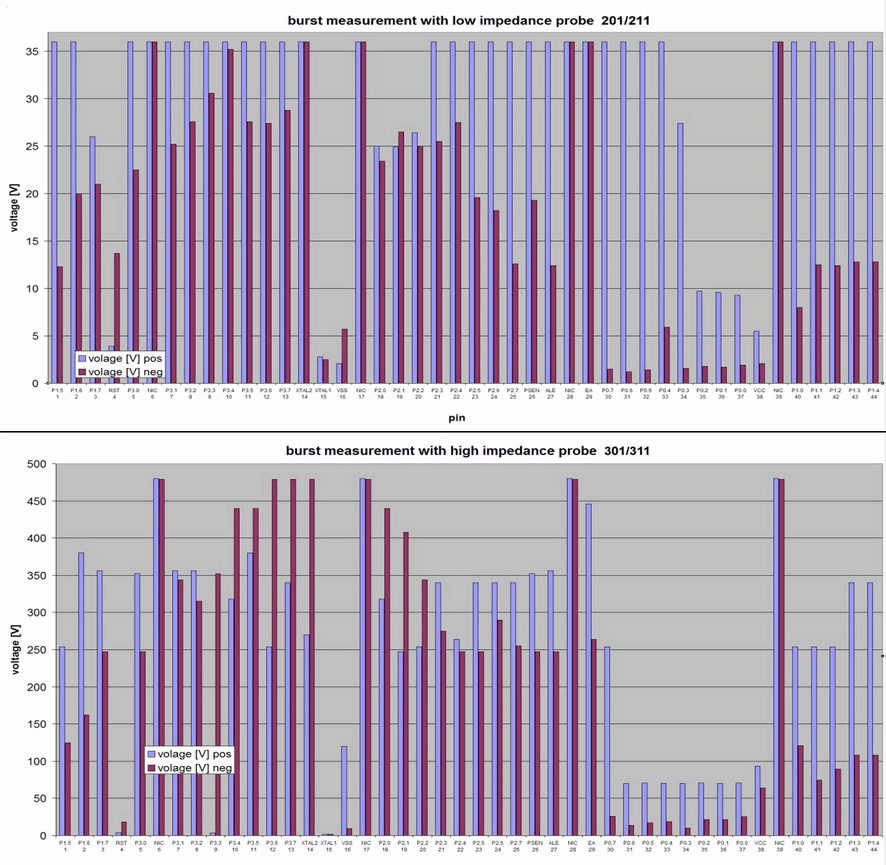

Im Bild 7 sind die pingranularen Störschwellen eines ICs dargestellt. Mit etwas vergleichender Erfahrung kann man erkennen, welche Pins extrem anfällig sind. Exponierte Pins sollten > ±15 V Störschwelle der Low-Impedanz-Quelle aushalten und > ±150 V der High-Impedanz-Quelle.

Simulation mit IC-Testpulsen

Zur Abschätzung der Wirkungen der beschriebenen Testpulse kann man die Simulationsmodelle der Testpulse (Stimuli) nutzen, die in /1/ zur Verfügung gestellt werden. Damit ist jeder Hersteller von ICs oder ASICs in der Lage, sich mit der vorgeschlagenen Testmethode auseinander zu setzen. Interessant ist natürlich, was im Inneren der ICs während der Störbeeinflussung passiert und welche Schaltungsteile in welcher Form beeinflusst werden. Dabei spielen interne parasitäre Elemente wie Leitungsinduktivitäten, parasitäre Kapazitäten und natürlich die realen Schutzstrukturen, die nur der IC-Hersteller kennt, eine wesentliche Rolle.

Bei der Fehleranalyse spielen neben der Signalverfälschung Störvorgänge im internen Versorgungssystem eine entscheidende Rolle. Externe Signalverfälschungen lassen sich im Allgemeinen mit Designmaßnahmen wie Telegrammwiederholungen, Fehlerkorrektur usw. beherrschen.

Nicht beherrschbar ist jedoch, wenn das Störereignis dazu führt, dass ein Teil der internen Versorgung zusammenbricht oder ins Schwingen gerät. Damit wird die Gesamtfunktion des ICs beeinträchtigt.

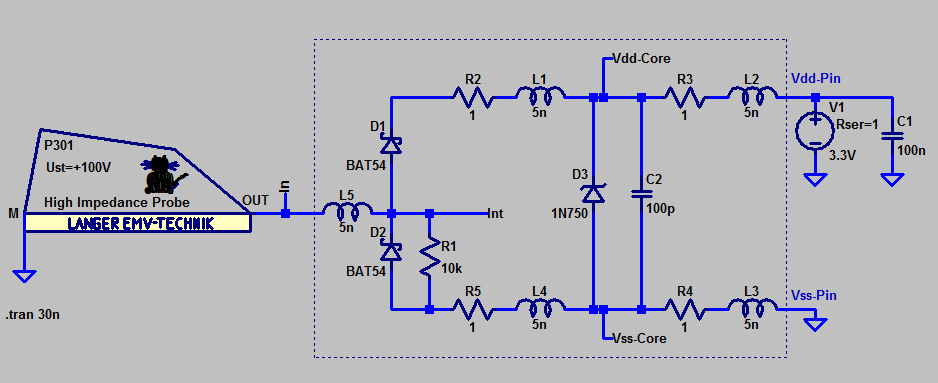

Im Bild 9 ist das LTSpice-Modell /1/ der High-Impedance-Probe P301 an den Eingang einer vereinfachten IC-Ersatzschaltung angeschlossen. Der Eingang besteht aus Schutzdioden D1 und D2, die mit dem Vdd und Vss-System des ICs verbunden sind. Den Core des ICs verkörpert die Ersatzkapazität C2 (100 pF), Die wichtigsten Schaltungselemente werden durch L1-L4 und R1-R5 und D1-D3 realisiert. Die Power-Clamp D3 schützt den Core vor Überspannung.

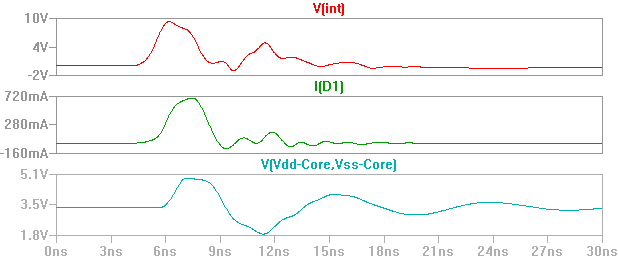

Bei einer Prüfspannung von +100 V entsteht im IC die Störspannung V(int) (Bild 10). Über die Schutzdiode D1 fließt der Strom I(D1). Der Strom lädt die Corekapazität um. Es entsteht im Inneren des ICs ein Einschwingvorgang auf dem Versorgungssystem V(Vdd-Core, Vss-Core) (Bild 10). Die Corespannung bricht dabei von 3,3 V auf 1,8 V ein und kann zum Ausfall des ICs führen.

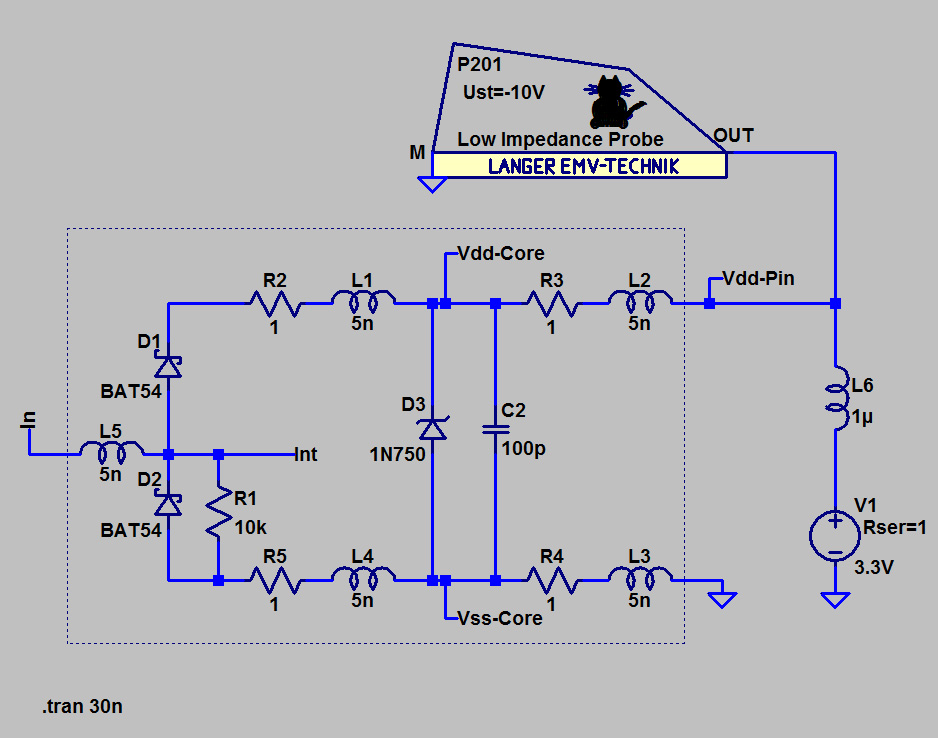

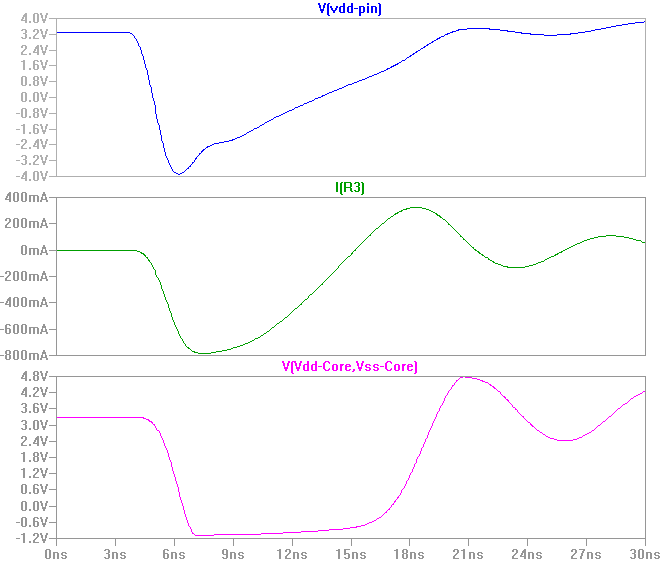

Im Bild 11 ist das LTSpice-Modell der Low-Impedance-Probe P201 /1/ an das Vdd-Pin der IC-Ersatzschaltung angeschlossen. Der Stützkondensator C1 wurde entfernt und durch die Probe P201 ersetzt. Weiterhin wurde das Versorgungssystem mit der Induktivität L6 entkoppelt. In der Probe P201 wurde eine Störspannung von -10 V eingestellt. Der Störvorgang erzeugt am Vdd-Pin einen Spannungseinbruch bis -4 V (Bild 12). Der Störstrom fließt hauptsächlich über die Power-Clamp D3 und die Core-Kapazität C2 zu Vss ab. Dabei bricht die Corespannung V(Vdd-Core, Vss-Core) bis auf -1,2 V ein. Die Funktion des ICs wird mit Sicherheit gestört.

Die anhand von Bild 10 und Bild 12 gezeigten Phänomene zeigen die Vorgänge in ICs nur beispielhaft. Es ist damit ein Lösungsansatz aufgezeigt, die hochkomplexen Störvorgänge in ICs durch Simulation zu verstehen.

Aus der Verbindung von LTSpice Simulation und Tests mit realen ICs und Probes (P201 und P301) sind effiziente Entwicklungswerkzeuge vorhanden, die EMV-Eigenschaften von ICs zu untersuchen und zielgerichtet zu verbessern. Durch die Verfügbarkeit der LTSpice-Modelle der Testgeneratoren wird der Zugang für die IC-Hersteller zum beschriebenen Testverfahren vereinfacht. In der Zukunft sollte es möglich sein, die EMV-Eigenschaften schon zu Entwicklungsbeginn von ICs spezifizieren zu können.

Literatur Teil 2:

| /1/ | LTSpice-Simulationsmodelle für IC-Testpulse P201 / P301: https://langer-emv.com/de/category/simulation/76 |